近來,Imec CMOS 技術高級副總裁 Sri Samavedam 與semiengineering坐下來討論 finFET 縮放、環柵晶體管、互連、封裝、小芯片和 3D SoC。以下是該討論的摘錄。

SE:半導體技術路線圖正朝著幾個不同的方向發展。我們有傳統的邏輯擴展,但封裝發揮了重要作用。這里發生了什么事?

Sri Samavedam :作為摩爾定律基礎的密度縮放將繼續存在。如果你看看芯片中晶體管的數量多年來是如何演變的,它非常接近摩爾定律。密度縮放正在按預期發生。但是我們看到的是,您沒有從我們過去使用的通用計算 CPU 中獲得性能。節點到節點的邏輯器件性能已經放緩。因此,您將不得不提出新的材料和設備架構,以在系統級別為您提供額外的性能提升。

在 Imec,我們還專注于 STCO,即系統技術協同優化。對此有兩種方法。我們有自下而上和自上而下的方法。通過自下而上,我的意思是您著眼于技術,而不僅僅是擴展以在系統級別為您提供性能。例如,您可能需要一種新的冷卻技術,使您能夠突破電源壁壘并為您提供系統級性能。

SE:您還看到了哪些其他趨勢?

Samavedam:我們觀察到的另一個趨勢是,多年來一直是通用計算的主力的 CPU 正在放緩。我們發現出現了更多特定領域的架構。GPU 就是一個很好的例子。您可以將 GPU 性能視為每單位面積的操作數或每單位瓦特的操作數的函數。例如,只需看看 Nvidia 和 AMD 的 GPU。他們繼續做得很好。它們利用可擴展性,可以為可并行化的工作負載(如圖形處理或機器學習)封裝更緊湊、更高效的內核。它們并沒有表現出我們在 CPU 中看到的同樣的性能下降。因此,我們希望看到更多特定領域的計算機體系結構向前發展。

SE:在晶體管方面,finFET 一直是高端的主力器件。FinFET 已縮小至 3nm。這里發生了什么事?

Samavedam:從 14nm 開始, FinFET 已經成為五代的主力器件。我們已經看到它在 14nm、10nm、7nm 和 5nm 作為代工產品。英特爾確實推出了 22nm 的 finFET。3nm 也將成為 finFET 節點,至少對臺積電來說是這樣。如果你想要邏輯縮放,你必須縮放標準單元庫。當您將標準單元庫從 7.5 軌(track)擴展到 6 軌或 5 軌時,可用于構建 finFET 的有源器件寬度正在減少。因此,您可以從 7.5 軌的三個鰭片到 6 軌的兩個鰭片,再到 5 軌的單個鰭片裝置。單翅片器件的可變性更大。這是 finFET 將停止擴展的原因之一。

SE:3nm 似乎是 finFET 的最后一個節點。我們開始看到向納米片 FET 的轉變,這是一種環柵 (GAA) 架構。這有什么好處?

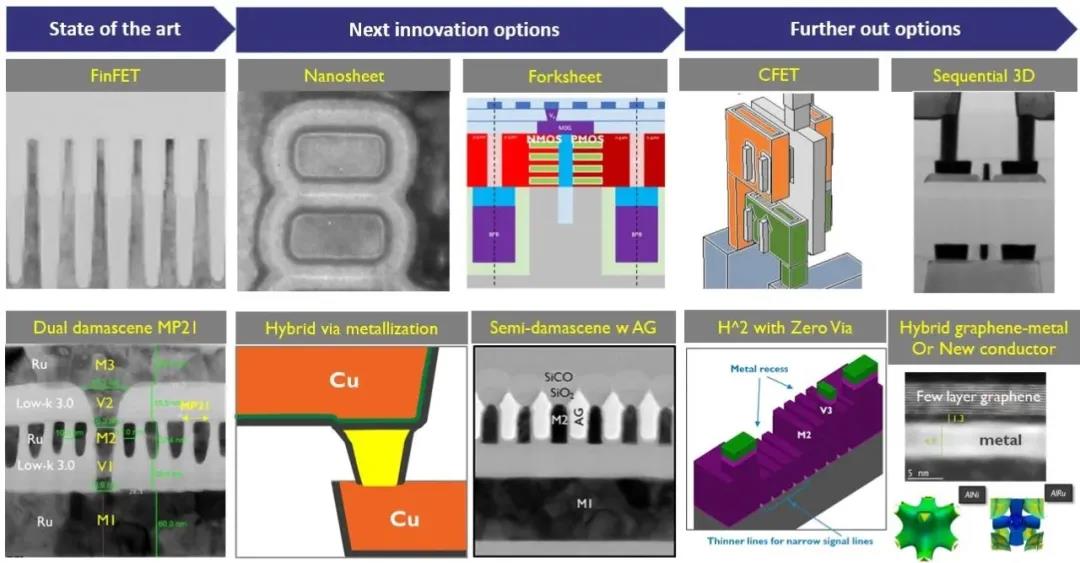

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?圖 1:晶體管(上圖)和互連技術(下圖)路線圖。資料來源:IMEC

Samavedam:如果你用一堆納米片代替單個鰭片,你可以獲得更大的每個封裝寬度,并且每個封裝可以獲得更多的驅動電流。這就是您看到從 finFET 向納米片過渡的原因。使用納米片,您可以構建高性能的 5 軌庫。納米片也是GAA設備。

如果您用柵極圍繞溝道,您將獲得更好的柵極控制,與 finFET 相比,您可以將柵極長度縮放得更多。FinFET 是三柵極器件。他們在溝道的三個側面都有一個柵極,而不是四個側面。通過縮小鰭片間距,FinFET 一直在縮小,從 14nm 縮小到 3nm。您可以通過縮放鰭片間距獲得更多的鰭片,您還可以縮放鰭片高度以獲得更大的器件寬度。

達到3nm之后,您將達到鰭片高度的極限。隨著鰭變高,您可以增加驅動電流,但也存在電容損失。如果驅動電流增加不能抵消電容損失,那么繼續縮放鰭片高度是沒有意義的。當您使 finFET 結構更高并且鰭之間的空間由于鰭間距縮放而縮小時,將柵極電介質和金屬層包裹在鰭周圍更具挑戰性,因為您可以在寬松的尺寸下做到這一點。因此 finFET 微縮變得更具挑戰性,而納米片為您提供了一種在相同占位面積內獲得更多驅動電流的方法。

SE:納米片 FET 的其他好處是什么?

Samavedam:讓我們看看 finFET。如果要增加器件寬度,則必須從一個Fin到兩個fin再到三個Fin。它是離散的。在納米片中,您將納米片堆疊在活動區域中。您可以改變納米片的寬度并獲得不同的器件寬度。這為您提供了設計的靈活性。如果您想要具有更高和更好驅動電流的晶體管或標準單元庫,您可以選擇更寬的表。如果您想優化電容和功率,您可以使用窄板。這是納米片為設計提供的額外靈活性。

SE:納米片的制造挑戰是什么?

Samavedam:形成這些納米片的方式是首先使用外延法沉積多層硅和硅鍺。然后,蝕刻出硅鍺層以獲得硅納米片。生長外延層是相當好的理解,但釋放這些納米片是一個挑戰。您必須確保硅鍺蝕刻對硅具有選擇性。它不能使留下的硅通道變得粗糙。你要確保它們不會粘在一起。當您蝕刻掉硅鍺時,尤其是在使用濕法蝕刻時,您需要確保薄片之間沒有靜摩擦。

SE:其他挑戰是什么?

Samavedam: 另一個挑戰更多的是性能挑戰。在 finFET 中,大部分電流傳導發生在 (110) 表面。fin的側壁是(110)。這是 PMOS 移動性的好平面。納米片是平的。它們遵循與基板相同的方向,因此是(100)方向。PMOS 在 (100) 方向上的驅動電流性能受到影響。為了恢復 PMOS 的性能,您必須在納米片中強調這些通道。將應力納入納米片是一項挑戰。形成多 Vt 器件是另一個挑戰。設置閾值電壓的方式是改變柵極功函數。因此,您可以在納米片之間加入不同的金屬層以獲得不同的閾值電壓。納米片之間的間距很緊。您需要蝕刻掉一層并沉積第二層以獲得不同閾值電壓的第二功函數材料。這很有挑戰性。

SE:晶圓廠工具準備好用于納米片了嗎?

Samavedam: 幾年來,人們一直在研究環繞式門結構。這些工具在支持納米片的單元工藝方面取得了長足的進步。計量學存在一些挑戰。在納米片器件的形成中,您有一個稱為內部隔離層的模塊,您試圖在其中將柵極與源極/漏極分開。您必須選擇性地蝕刻硅鍺層,然后用電介質填充它并形成間隔物。從計量學的角度來看,這是一個具有挑戰性的模塊。控制橫向硅鍺凹槽并形成內部間隔物,然后確保一切正常,具有挑戰性。人們使用散射儀或光學 CD 來測量這些結構。有時,您可能需要結合計量技術來很好地處理過程控制。但總的來說,工具可用。硅鍺相對于硅的選擇性蝕刻是一個重要的模塊。該工具在開始時不可用。現在,如何做到這一點已經眾所周知。

SE:在納米片中,EUV 光刻將圖案化片。這里有什么挑戰嗎?

Samavedam:您將不得不使用單打印EUV,具體取決于您圖案的間距。單純從光刻的角度來看,現在EUV光刻已經成熟,可能不會有太多的挑戰。納米片蝕刻可能仍然是一個挑戰,因為要圖案化多個層。

SE:在先進的晶體管中,生產線的后端 (BEOL) 存在一些重大挑戰,即在哪里制造互連,對嗎?

Samavedam:我們的觀點是銅雙鑲嵌將縮小到約 21nm 間距。但該行業面臨的挑戰在于阻力。當您縮小間距時,通孔電阻會起飛。我們一直在尋找減輕通孔阻力的方法。你可以通過幾種不同的方式來做到這一點。您可以選擇性地沉積不同的材料,例如釕、鉬或鎢,這樣您就可以使用不同的銅線通孔材料。

另一種方法是縮放襯墊/阻擋材料,以便在通孔中有更多的銅空間。你可以這樣做到 21nm 間距。如果你想縮小到 21nm 以下,我們相信你必須去直接金屬蝕刻。這就是我們所說的半鑲嵌集成。有些人也將其稱為減材金屬化。您通過直接金屬蝕刻來定義線條。你可以形成高縱橫比的線條,這樣你就可以獲得低阻力的線條。

但是當你走高縱橫比的線路時,電容是個問題,因為兩條線路之間有很多重疊區域。為了緩解這種情況,我們計劃引入氣隙以降低電容。如果要在半鑲嵌集成中進行直接金屬蝕刻,則必須使用易于蝕刻的金屬。銅不是其中之一。這就是我們選擇釕的原因。與銅相比,釕更容易蝕刻,而且隨著線寬的縮放,它的電阻也很低。

SE:我們能夠將納米片縮放到多遠?Imec 的forksheet FET 技術在哪里發揮作用?

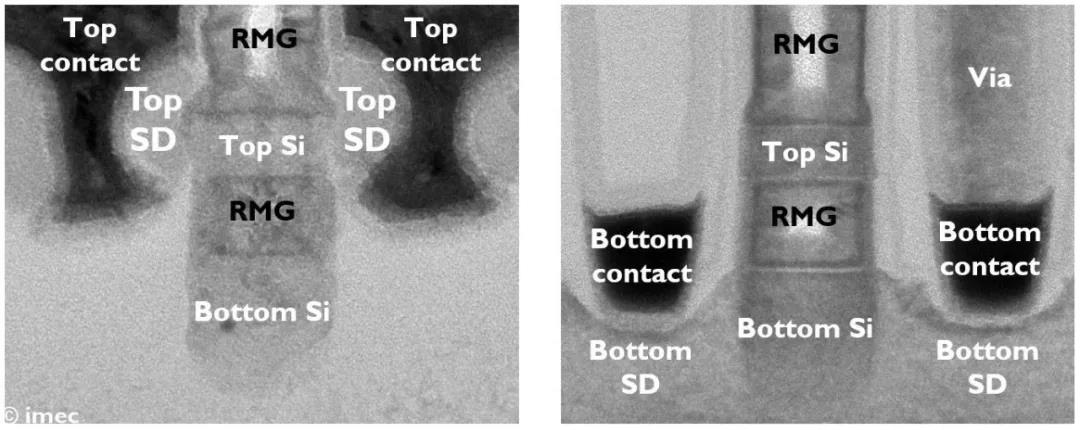

Samavedam:forksheet FET是 Imec 的一項創新。隨著您繼續縮放軌道高度,您正在減少設備可用的有效寬度和標準單元的驅動強度。這就是為什么隨著軌道高度的縮放,納米片優于 finFET 的原因。但是,當您嘗試進一步擴展軌道高度時,即使是納米片也會失去動力。您可以縮放標準單元中 NMOS 器件和 PMOS 器件之間的 n 到 p 空間,以創建更多的有源器件寬度。您可以通過蝕刻和形成狹窄的介電壁來縮放該空間。這就是forksheet設備的由來。

與納米片相比,它在相同的占位面積內為您提供了更大的有效寬度,并且它還具有更低的寄生電容,與納米片相比,它具有約 10% 的性能優勢。它使用了我們已經用納米片建立的許多集成基礎設施。這是一種將納米片延長一代的方法。在納米片和叉片之間,我們相信還會有大約三代。所以我們將有 2nm 和 14 埃的節點,并且可能有 10 埃的節點,帶有納米片和forksheet。

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 圖 2:Imec 的forksheet FET

SE:封裝和小芯片在哪里適合?

Samavedam:當今有許多使用 2.5D 或 3D 集成的高性能系統。在某些情況下,公司采用 SoC 并將其劃分為不同的功能,例如邏輯、內存和 I/O。這些功能中的每一個都是使用不同的小芯片構建的。有時,它們使用不同的 CMOS 技術。他們使用不同的 3D 互連技術將它們組合在一起,例如中介層、芯片到晶圓微凸塊鍵合或芯片到晶圓混合鍵合。我們將此稱為小芯片方法。這發生在高性能領域,最終會滲透到移動應用程序中。

SE:所有這些都將走向何方?

Samavedam:當今業界采用的方法是小芯片方法。每個芯片單獨設計并封裝在一起。我們設想的是真正的 3D SoC,其中邏輯和內存芯片是共同設計的。為此,您需要新的 EDA 工具功能。在真正的 3D SoC 設計中,布局布線和時序收斂可以在兩個芯片中同時發生。今天,在小芯片方法中,您需要一條總線來連接小芯片。這增加了塊之間的延遲,而且效率不高。如果您能夠共同設計小芯片,并且能夠作為單個 SoC 進行布局布線和時序收斂,那么您將獲得更高效的緊湊型設計。您可以避免冗余緩沖區,并且不必像在當前小芯片方法中那樣擔心這兩個塊之間的延遲。我們一直在與 Cadence 合作。他們提出了一個工具流程,使您能夠在小芯片之間進行真正的 SoC 3D 協同設計。我們將看到更多這種方法的例子。3D SoC 方法需要時間,因為 EDA 工具才剛剛啟用。

SE:3D 封裝和 3D SoC 的另一個推動因素是縮放凸塊間距,對嗎?

Samavedam:我們已經在研究中證明了微凸塊的間距低至 10 微米,甚至 7 微米。但是,如果您查看生產中的微凸塊,它們會在大約 30 微米間距處飽和。如果系統公司有足夠的推動力來擴展互連密度,那么您將看到來自OSAT的更多產品。為了實現這些緊密的微凸點間距,設備生態系統需要成熟一點。我們正在與設備供應商合作來做到這一點。一旦啟用了 EDA 工具,系統公司將開始推動更密集的互連。然后,您將開始看到更多來自 OSAT 的密集互連產品。

SE:混合鍵合怎么樣?

Samavedam:今天,有幾個混合鍵合的例子在生產中。圖像傳感器產品使用它。YMTC 使用混合鍵合來連接 3D NAND 中的外圍邏輯和內存。這是當今的晶圓級技術。您需要干凈的 CMP 表面才能獲得良好的混合鍵。如果您在晶圓級進行,則頂部裸片和底部裸片的尺寸需要匹配。這是制約因素之一。如果是晶圓級工藝,晶圓廠比 OSAT 更有可能提供這種技術。有芯片到晶圓混合鍵合的例子。AMD和臺積電最近公布了一個例子。這就是芯片到晶圓級混合鍵合的一個例子。

SE:混合鍵合的挑戰是什么?

Samavedam:你需要極端的平面性。這是一個約束。為確保良好的混合鍵合,您需要與銅兼容的電介質。我們使用銅和碳化硅作為電介質。SiCN 是一種低溫沉積電介質。這給了我們最好的粘合性能。準備用于混合鍵合的銅 SiCN 表面仍然是一門藝術。CMP 中需要許多工藝優化。您必須使用多個 CMP 步驟。您需要非常好的局部平面度以及全局平面度,尤其是在晶圓級進行時。CMP 控制和具有適合混合鍵合的電介質是兩個關鍵要求。

SE:您如何定義 3D SoC?

Samavedam:您可以在 2D SoC 中劃分不同的功能,如內存和邏輯,并分別設計它們。這就是小芯片方法。我所說的 3D SoC 是指您將內存和邏輯芯片共同設計為單個 SoC。連接可以在更密集的級別,您不必擔心兩個芯片之間的額外通信開銷。是直接通信。您不需要額外的 IP、PHY 或兩個小芯片之間的通信總線。您可以在 3D SoC 中實現更細粒度的分區。為此,您需要更密集的互連。您還需要 EDA 工具來支持這種協同設計。

SE:我們會看到具有2D材料的 CFET 或器件嗎?

Samavedam:2D 材料很有前景,因為它們具有高遷移率。它們可以形成非常薄的原子通道,因此您可以更積極地縮放柵極長度。但是,您還必須解決幾個基本的材料問題。你必須提高源漏區的溝道遷移率和接觸電阻。我們不知道如何在這些 2D 材料上很好地縮放柵極電介質厚度。我們構建這些設備的方式可能完全不同。未來幾年有很多問題需要回答,以了解這些材料是否足夠真實以使其成為路線圖。

SE:CFET 呢?

Samavedam : 使用CFET,代表互補 FET,N 和 P 器件構建在彼此之上。在過去的幾年里,Imec 已經展示了 CFET 的概念。英特爾在 2019 年和 2020 年也有幾篇論文。CFET 的挑戰在于集成。集成很復雜,形成 CFET 的方式也不同。您可以以單片方式進行,在同一步驟中形成頂部有源區和底部有源區,并使用通用自對準柵極連接兩個器件。這里的挑戰是需要許多新的復雜單元工藝,如高縱橫比圖案化、高縱橫比沉積等。或者您可以按順序進行。在這種方法中,您構建一個設備并結合不同的晶圓來處理下一個設備。您可以為頂部設備使用不同的基板方向或不同的通道材料,其挑戰是將頂柵連接到底柵,因為它們不是自對準的。還需要擔心頂部設備的熱預算對底部設備的影響。頂部和底部晶圓之間的無空隙鍵合以及其間的薄電介質也非常具有挑戰性,因為沒有好的工具來檢測這些微空隙。這就是順序 CFET 集成的復雜性。我們正在制定這兩個計劃。從設備性能的角度來看,我們相信它們可能非常相似。我們可以優化架構以使它們具有相似的性能,但它們各自的集成復雜度不同。所以這就是我們現在正在努力解決的問題。

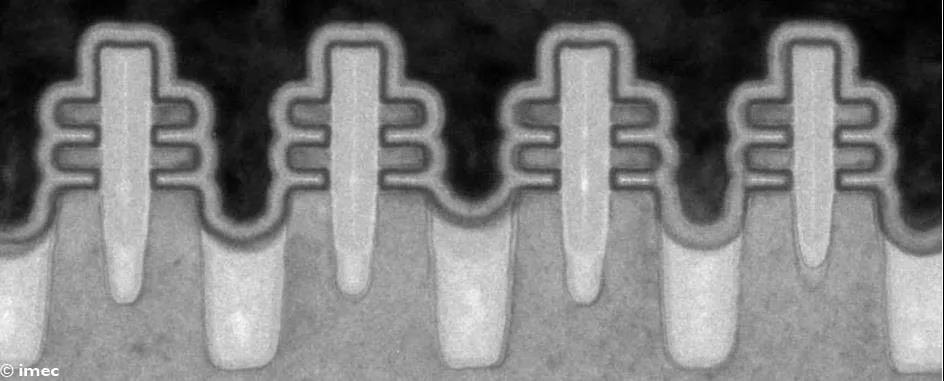

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 圖 3:CFET 運行。資料來源:IMEC

SE:傳統的邏輯擴展和封裝/小芯片或多或少是并行路徑,對嗎?

Samavedam:它們將同時發生。SoC 的某些組件的擴展性不是很好。例如,I/O 或 SRAM 不能與邏輯節點一起擴展。因此,它們可以使用更成熟的節點制造,并使用小芯片方法以具有成本效益的方式進行分區。將 SoC 劃分為邏輯和內存是增加內存帶寬以提高整體系統性能的另一種方法。小芯片方法和 3D SoC 方法是傳統邏輯縮放的并行路徑。

SE:這一切都將走向何方?

Samavedam:我沒有看到設備和材料或密度縮放方面的創新放緩。我們知道高 NA (0.55) EUV 即將到來。與當今 0.33 NA 的 EUV 相比,這將以更具成本效益的方式實現更密集的圖案。擴展以及設備架構創新將繼續進行。小芯片方法或 3D SoC 方法將并行發生,以支持未來的系統擴展。它們都將共存。